記事作成日時:2023-06-15 17:27:24

最終更新日時:2023-09-01 19:58:10

最終更新日時:2023-09-01 19:58:10

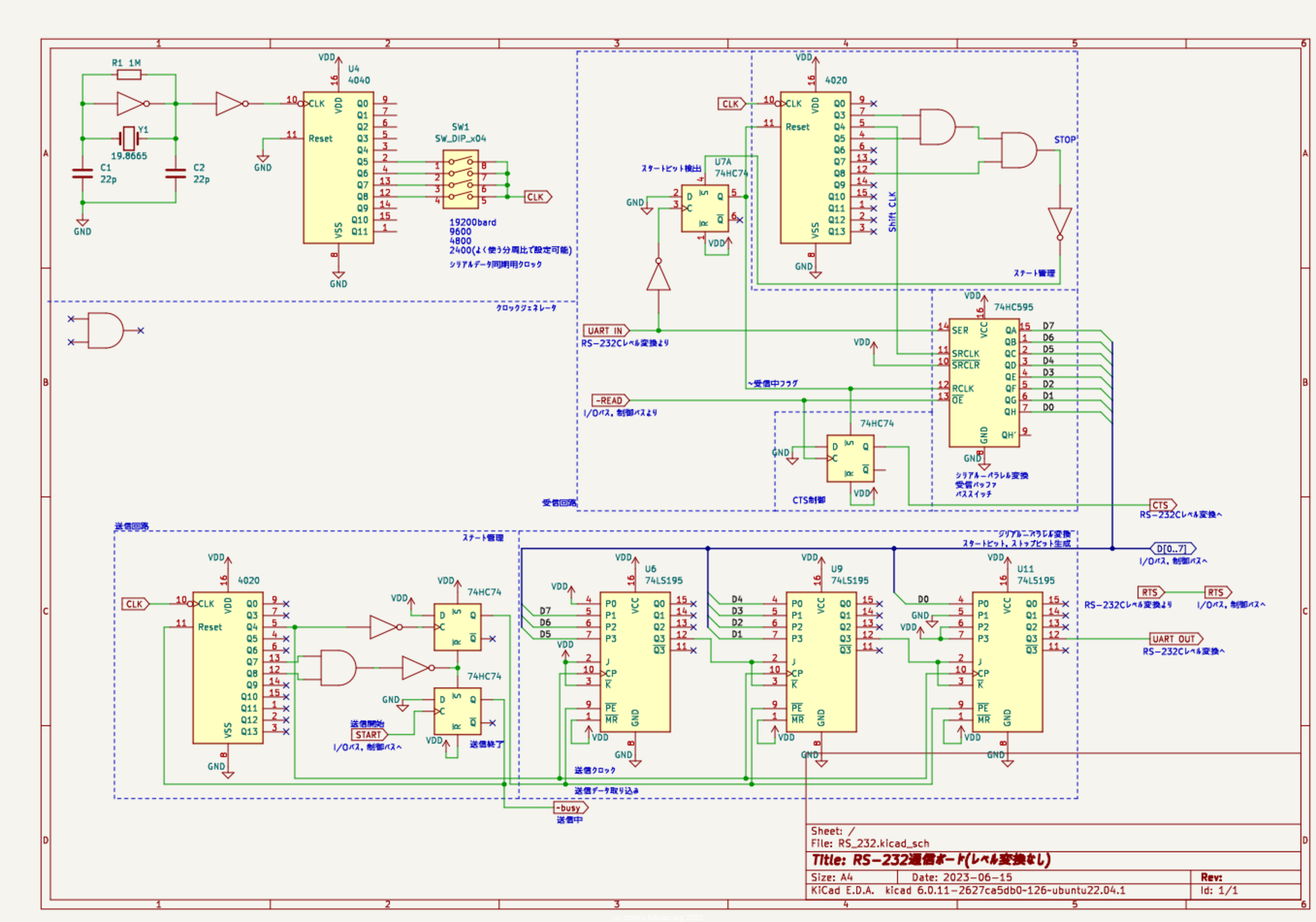

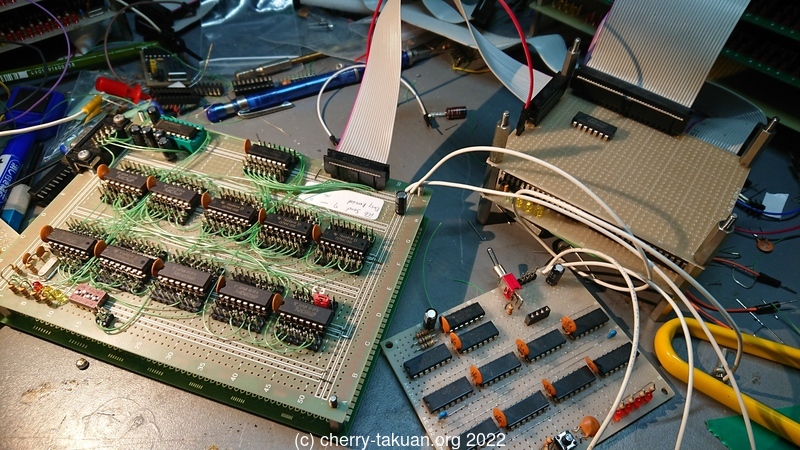

NLP-16のI/OとしてRS-232Cを使用した通信モジュールを作ってみたので回路図の掲載とその解説.

このモジュールは例のごとく汎用ロジックICのみで製作している.

過去の回路図では4020の接続,水晶の周波数に誤りがありました...修正版を上げなおしたのでご確認ください...

RS-232Cとは

RS-232Cとは

RS-232Cとは

米国電子工業会(EIA)によって標準化された、最高通信速度115.2kbpsのシリアルインターフェースの規格のことである。EIA-232と呼ばれることもある。www.sophia-it.com/ より引用(最終確認2023/06/15)

ものらしい.

様々な機器の制御やパソコン通信などでのモデムとの接続に使われていて,最近は見かけないがノートPCなどにもついていた.

動作が単純でかつ現代のパソコンからでも容易に扱えるためNLP-16などの自作CPUとの通信に応用するのに向いていると考える.

(諸説があるので十分に調べるまではこの程度の言及にとどめます.)

データ

データ

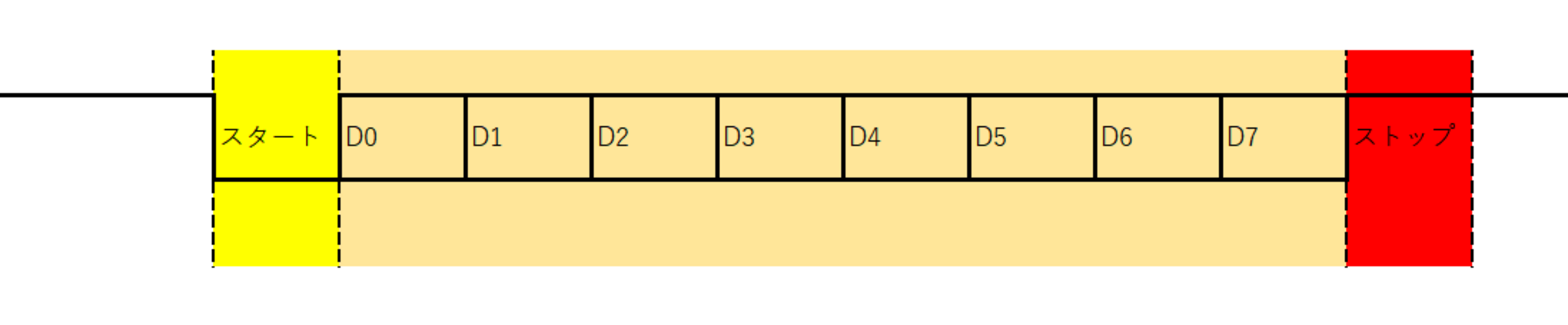

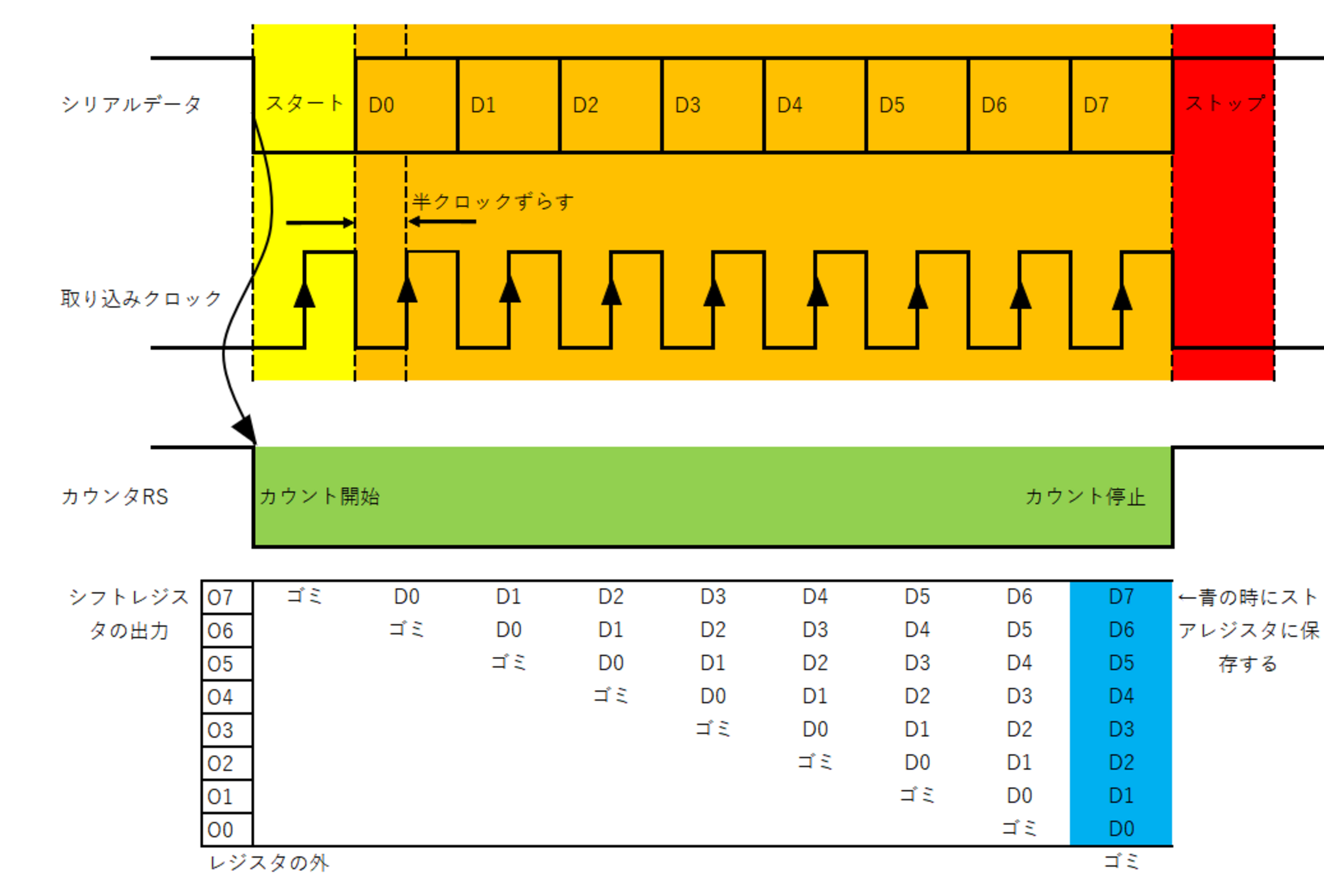

早速だが,目標とする送受信データはこのような感じ.(左から右へと時間が流れる)

RS-232Cなどに用いられるシリアル通信のフォーマットには様々な種類があるが,ここではパリティ無し,ストップビット1bitの形式を時系列で説明する.

受信側

受信側

受信側はこんな感じの動作を行う.

①Hレベルでは待機状態(白色)

②信号線がLになった場合,スタートビット(黄色)としてデータの取り込みを開始

③データの受信を開始すると下位ビットから取り込んでいく

④ストップビット(赤色)を確認して受信を終了

以上が受信の流れ.

簡単に言ってしまえば,スタートビットが来たらそれに合わせて8回データを取り込めばいいわけだが,安定してデータを取り込むには取り込むタイミングにちょっとだけ工夫がいる.

具体的には以下のようになる.

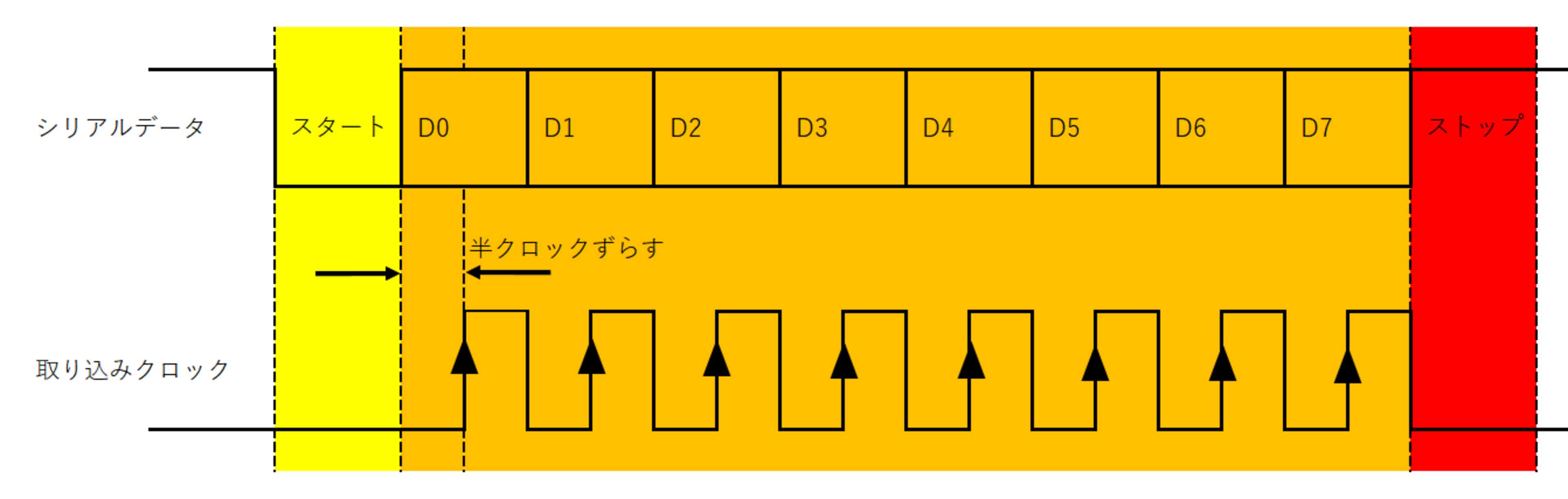

先ほどのタイミング図にデータの取り込みクロックを追加した.

工夫というのはこの取り込みクロックが真ん中に来るようにしている点だ.これがなぜ工夫になるかというと,送信側も受信側も誰もが目を奪われてく完璧で究極のクロックを持っているわけではなく,若干ずれている.

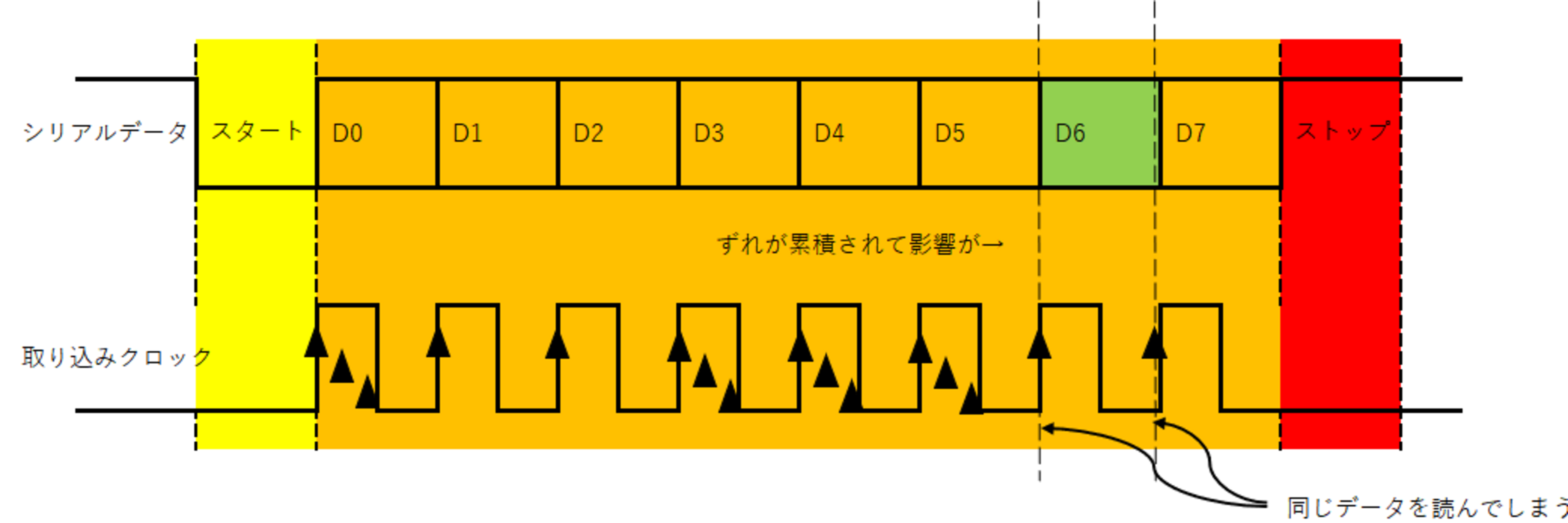

ずれているとスタートビットで同期を取った直後はデータが切り替わるちょうどに取り込めて問題がないが,例えば受信側が送信側よりクロックが早ければこのようなギリギリのタイミングでは一つ前のデータを取り込んでしまう可能性がある.(そもそもそんなぎりぎりにやる意味がない)

というわけで半クロックの待ちを入れてからデータを取り込むのが常套手段になっているのでそれに倣って設計する.(高級なものでは一つの区間で奇数回取り込んで多数決で決定したりもするらしい)

スポンサードリンク

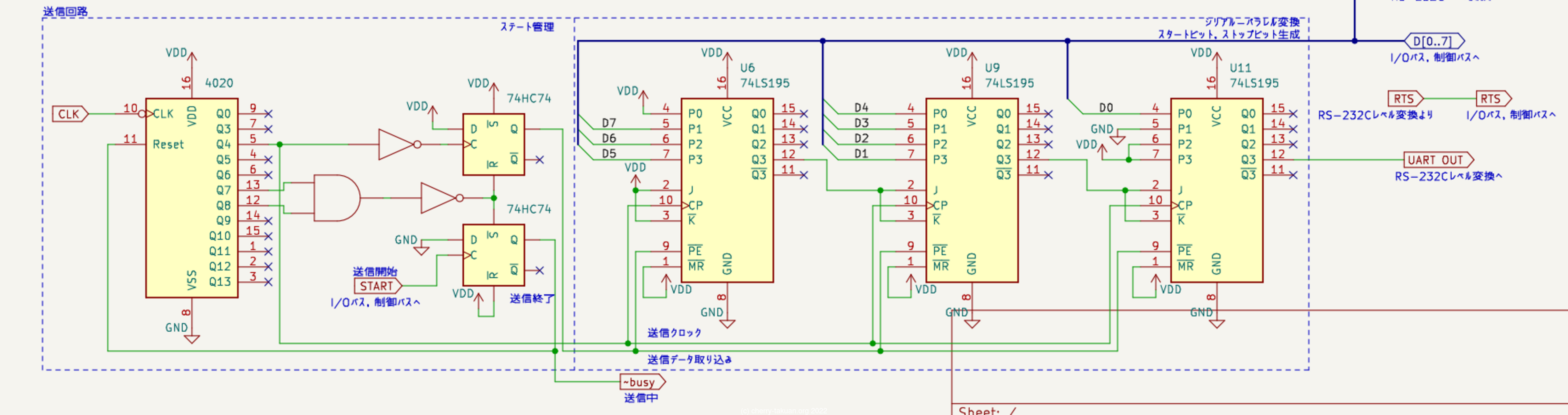

受信回路

受信回路

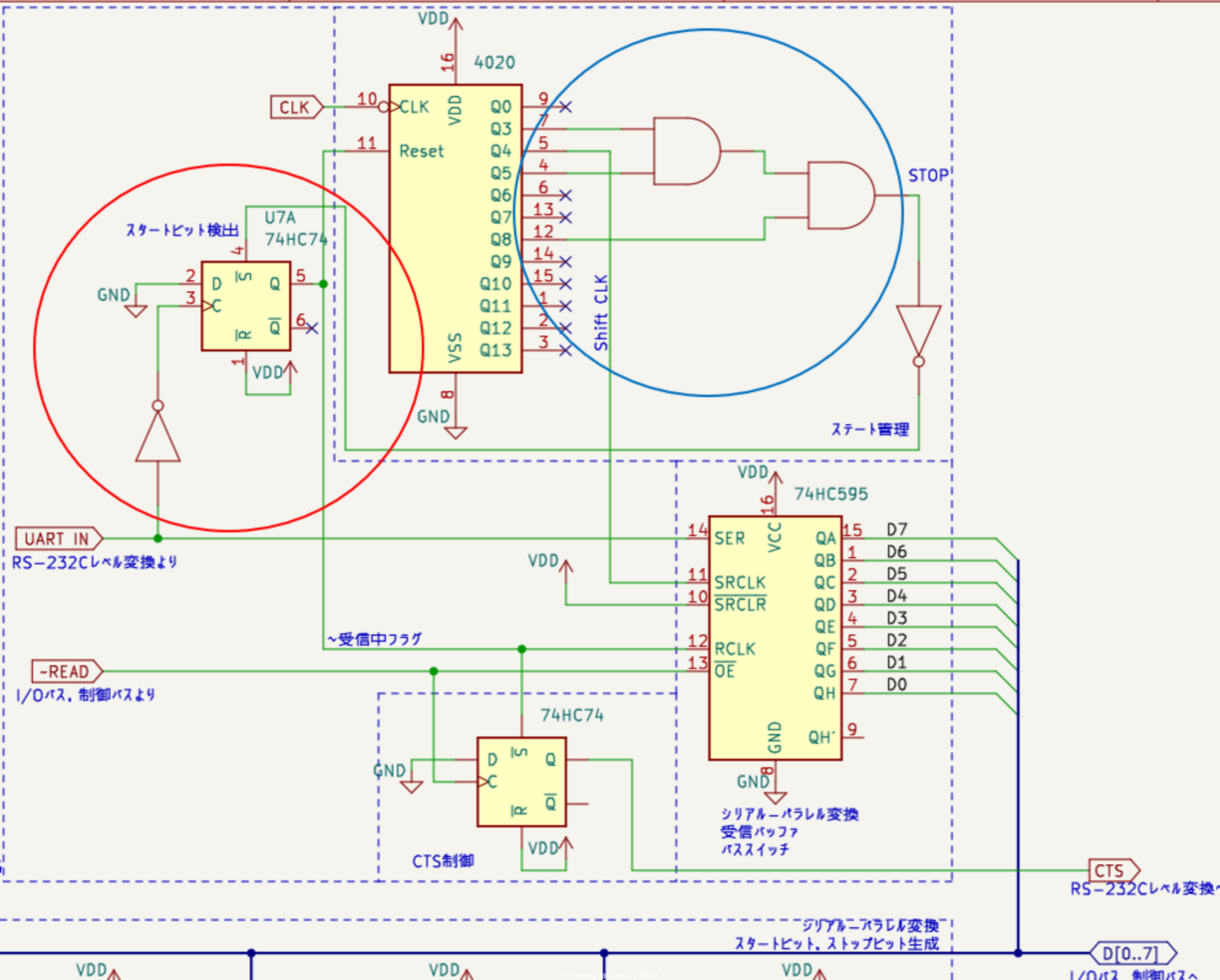

実際に制作した受信回路はこのようになっている.

QがLになるとバイナリカウンタの4020はカウントを開始して,受信回路のタイミングを刻み始める.ここでこの受信のタイミングは半クロックの遅延が必要と先に述べたが,コレは4020の非同期RSをいい感じに使った例である.

話は簡単で,カウントが0の状態からカウントアップしていけば1周期の半分で出力が立ち上がるわけだから,カウンタの値を常に0にして待っていて,データが立ち下がったその刹那,カウント開始してやればちょうど真ん中でカウンタの出力が立ち上がる.このようにすればステートの管理などは特に必要もなく,だいたい真ん中で立ち上がるデータ取り込みのクロックが生成できる.

この説明通りのタイミングでは以下のようになる

そう,困ったことにスタートビットの期間でも取り込みが発生してしまい,「ゴミ」が取り込まれる.

しかし心配することなかれ,シフトレジスタに入っているデータを追っていけば問題ないことがわかる.

ゴミがあっても データの期間に8回クロックを入れてやれば先頭のゴミはシフトレジスタ外に消えてなくなる ため,カウンタがRSしてから正味9回のクロックで正常な8ビットのデータが得られる.詳しくは図を見てください.

受信回路の青丸 の部分のQ8 & Q5 がこの9回のカウントをしていて,Q4が取り込みクロック.Q3もアンドに含めているのは9回分のクロックがQ4が確実に出てくるのを待つため.9回クロックが出てくることを確認(回路図中のSTOP)するとD-FFのQをセットし,カウンタをRSする.

最後に全く説明していなかったハードウェアフロー制御だが,受信回路のデータが読まれる前にさらにデータを送られると保存しておけないため非常に嫌だ.つまり,データが読み取られるまで送信元に「これ以上送るな」と教える必要がある.これがハードウェアフロー制御.

回路図中のCTS制御と書いてある部分がそれであり,受信時にD-FFをセットして,READでデータが読まれるとクリアする.

ここでREAD(OE)は負論理であるため,Lの時にデータが出力される.つまり,データの読み取りが完了するのはREADが立ち上がったタイミング. 奇跡的に7474(D-FF)は立ち上がりでデータを取り込む のでREADにD-FFのクロックを直結すれば読み取り完了と同時に送信元に「送信可」を伝えられる.

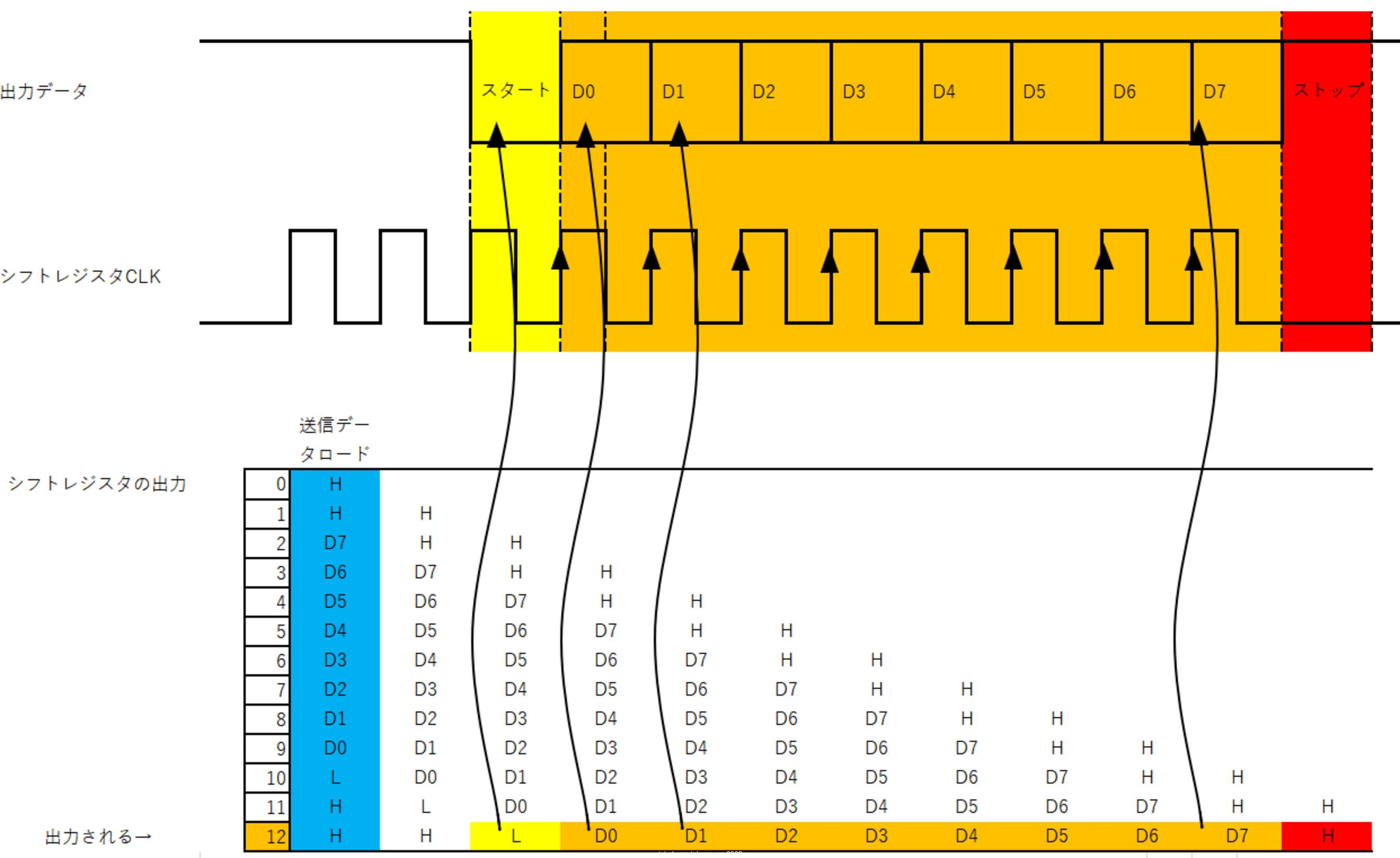

送信側

送信側

送信側は受信側よりもシンプル.回路は以下のようになっている.

全部一緒くたにすることで一回ロードしてしまえばあとはタイミングよくシフトしていくだけで済む.

タイミングチャートはこんな感じ.

ロジックICのみのRS-232C(信号レベル的にはUART)の回路

ロジックICのみのRS-232C(信号レベル的にはUART)の回路

↓これらを組み合わせると回路はこんな感じになる.なお,レベル変換の部分は書いていない(書き忘れた)ので各自MAX232等で適切にレベル変換を行ってください.はい.

関連するページ

-

電子工作 修理 TOP ここでは私が製作した物や修理したものについて書こうと思う。記事の内容については責任を一切負うつもりはない。 主な製作の方向性は私が製作したいと思えたものを作っている。そこには何ら崇高な目的も技術的に重要な要素もない。欠片もない。一個人での開発の集積場であり、何かを啓発するつもりもない。...(以下略)

記事作成日時:2022-02-27 15:41:38

最終更新日時:2022-02-27 17:30:32

-

RS-232C通信ボードをロジックICのみで作った NLP...(以下略)

記事作成日時:2023-06-15 17:27:24

最終更新日時:2023-09-01 19:58:10