記事作成日時:2022-04-15 12:53:03

最終更新日時:2023-03-19 21:01:28

最終更新日時:2023-03-19 21:01:28

NLP-16の概要

NLP-16の概要

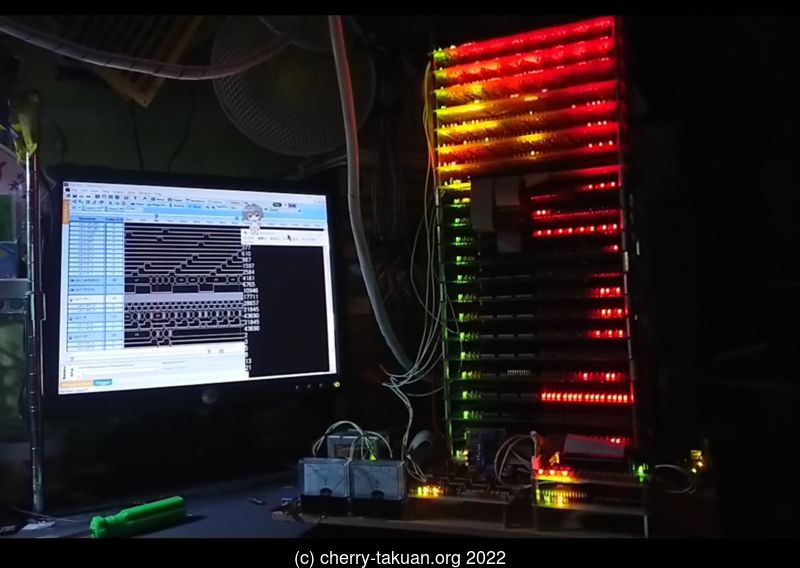

まずはこのCPUの概要を載せておく。

今度ほかのCPUとの比較表を作りたい。

このデータは暫定です。コロコロ変わるかも

| CPUバス幅 | 16bit |

|---|---|

| アドレス幅 | 16bit+バンク16bit(実行可能なページは0のみ) |

| アーキテクチャ | ノイマン型 |

| 動作クロック |

100kHzでの動作を確認。 それ以上は未計測。 |

| 汎用レジスタ | 16bit幅x5 |

| 演算機能 |

19種

算術演算は整数値のみ

符号付数値は2の補数表現 |

| 命令 | 可変長(1word~3word)全54種 |

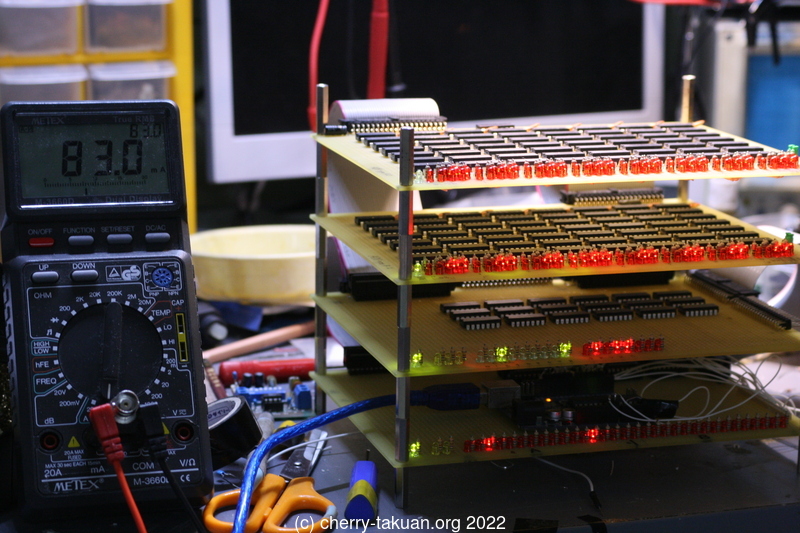

| 74HC00使用数 |

2022/04/15時点 812個(NANDとしては3200ゲートくらい) 2022/09/19時点 |

| 消費電力 |

2000mW

ほとんどLEDの消費 2022/04/15時点 |

不明な点があればBBSだったりTwitter、メールでどうぞ

※1 デバッガ使用時なので純粋に1kHzではない

バスのパルス幅から連続で命令を実行できたと仮定した場合の値

1命令ごとにPCとの通信待ちがあるため実際にはだいぶ遅い

これの説明はちょいと面倒なので別記予定

ある程度完成したため現在ではきちんとした方法で計測を行い100kHzでの動作を確認しています。

現在の作業進捗

現在の作業進捗

ALU製作 → 完了

レジスタ製作 → 完了

レジスタ制御 → 完了

ALU制御 → 完了

デバッグ環境構築 → 完了 随時アップグレードが必要

制御 →

作業中

完了

NLP-16の詳説

NLP-16の詳説

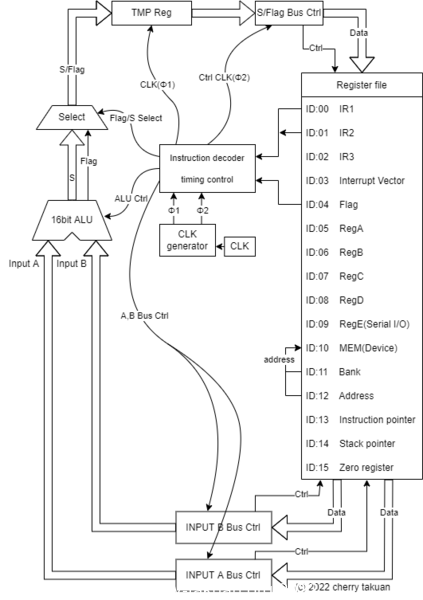

まずはアーキテクチャのブロックチャートをどうぞ

オレオレ仕様な図なんでちょいとわかりにくいかもしれないけど我慢して

クリックすると大きい画像が開きます。

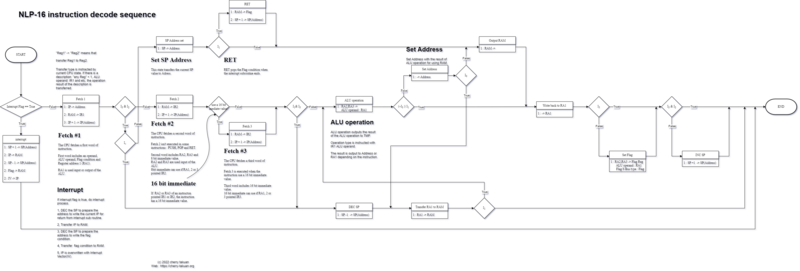

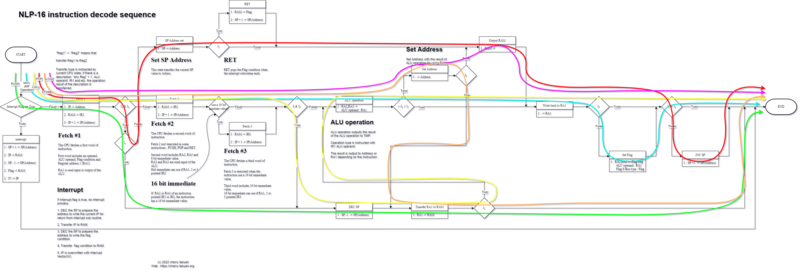

命令デコーダのデコード順序も書いたので良ければ

このフローに従ってデコードしていく(このフローチャートだけ見ても情報が不足している)

色分けをして各種命令のデコード順序を示す。

関連するページ

-

NAND(74HC00)だけで16bitCPUを作る[NLP-16]

このページはNAND素子のICである74HC00のみを用いて16bitCPUを作るという馬鹿みたいなことを纏めたページ。 また、早速だが使っているICは7400ではない。以前は”7400でCPUを作りたい”にしていたが詐欺なので変えた。 使用しているのはC...(以下略)

記事作成日時:2022-02-27 15:47:09

最終更新日時:2023-09-12 03:59:52

-

NLP-16 CPUの仕様 まずはこのCPUの概要を載せておく。今度ほかのCPUとの比較表を作りたい。...(以下略)

記事作成日時:2022-04-15 12:53:03

最終更新日時:2023-03-19 21:01:28

-

電子工作 修理 TOP ここでは私が製作した物や修理したものについて書こうと思う。記事の内容については責任を一切負うつもりはない。 主な製作の方向性は私が製作したいと思えたものを作っている。そこには何ら崇高な目的も技術的に重要な要素もない。欠片もない。一個人での開発の集積場であり、何かを啓発するつもりもない。...(以下略)

記事作成日時:2022-02-27 15:41:38

最終更新日時:2022-02-27 17:30:32