記事作成日時:2024-07-21 00:23:36

最終更新日時:2024-07-21 01:50:22

最終更新日時:2024-07-21 01:50:22

ここではNLP-16Aで使用しているALUの概略を載せています。まだ記事が書けていなくて図のリンク先はGithubの回路図に直接飛びます。後で書く。多分。

以上の演算の内,算術シフトにするか否かは回路図の1ページの57Aから57Dで行っています。算術シフトでは最上位ビット(符号ビット)が変化しないのですが,この回路回路によってボードが最上位バイトかつ算術演算時のみ最上位ビットが入力値スルーになるようになっています。

8bitの基板2セットで構成されているため,MSOピンによって最上位バイトであるかどうかを判断しています。

また,1ページ目の点線で囲まれた箇所は図中の制御バスをそれぞれのALUに分配するためのバッファとなっています。バッファを設けることでALU制御回路のファンアウトを下げています。

ALU

ALU

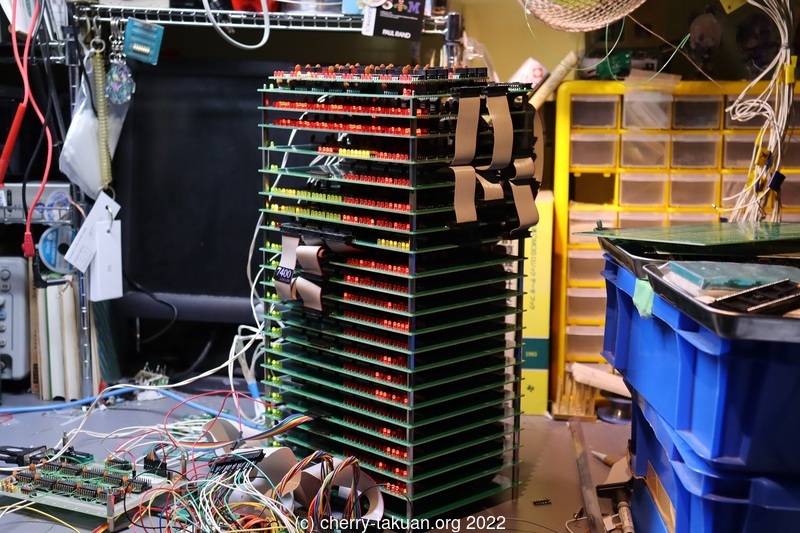

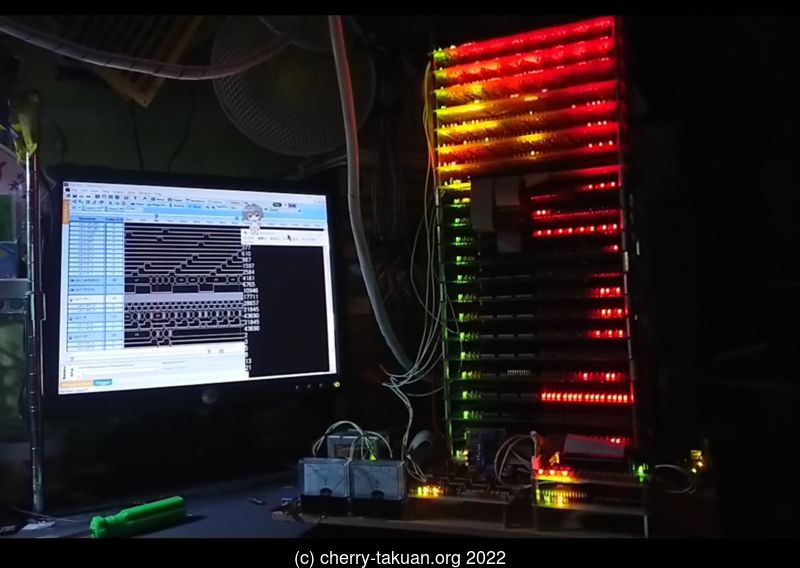

上にある二つの枠がそれぞれ8bitのALUです。このALUを2台並列に接続することで16bit ALUを構成しています。この8bit ALUにはさらにそれぞれの中に1bitのALUがあり,実質的にはこの1bitのALUを16セット並列に並べていることになります。

この1bitのALUは回路図中では2から9ページ目にあたります。実行できる演算は以下の通りです。

- ADD

- SUB

- OR

- NOT

- XOR

- INC

- DEC

- 算術左シフト

- 算術右シフト

- 論理左シフト

- 論理右シフト

- 左ロール

- 右ロール

- 入力スルー

以上の演算の内,算術シフトにするか否かは回路図の1ページの57Aから57Dで行っています。算術シフトでは最上位ビット(符号ビット)が変化しないのですが,この回路回路によってボードが最上位バイトかつ算術演算時のみ最上位ビットが入力値スルーになるようになっています。

8bitの基板2セットで構成されているため,MSOピンによって最上位バイトであるかどうかを判断しています。

また,1ページ目の点線で囲まれた箇所は図中の制御バスをそれぞれのALUに分配するためのバッファとなっています。バッファを設けることでALU制御回路のファンアウトを下げています。

ALU制御回路

ALU制御回路

ALU制御回路は主に命令デコーダから来る制御信号をALUが実際に解釈可能な制御信号に変換することとフラグの生成を行っています。

信号の変換は回路図2ページ目で行っていて,命令デコーダから来る6bitの信号とフラグレジスタの状態などの信号をいい感じに変換しています。

命令デコーダから直接ALUを制御できるように作ろうとすると命令デコーダの回路規模が大きくなり過ぎてしまうので一部を外側に出しました。

フラグはオーバーフローフラグ,キャリーフラグ,サインフラグ,ゼロフラグの4種を生成しています。(回路図4ページ目)

また,フラグはデータバスを通じてフラグレジスタに格納されるのでALUの演算出力と生成したフラグを選択するマルチプレクサも組み込んであります。

このマルチプレクサはちょっと手抜きをしているので下位4bitはちゃんとマルチプレクサになっていますが,フラグで使用しないそれ以外は常にALUの演算出力がそのまま出ています。

関連するページ

-

NLP-16Aアーキテクチャのページ ここではNLP...(以下略)

記事作成日時:2024-07-20 19:10:43

最終更新日時:2024-07-21 01:50:19

-

NAND(74HC00)だけで16bitCPUを作る[NLP-16]

このページはNAND素子のICである74HC00のみを用いて16bitCPUを作るという馬鹿みたいなことを纏めたページ。 また、早速だが使っているICは7400ではない。以前は”7400でCPUを作りたい”にしていたが詐欺なので変えた。 使用しているのはC...(以下略)

記事作成日時:2022-02-27 15:47:09

最終更新日時:2023-09-12 03:59:52