記事作成日時:2024-07-20 19:10:43

最終更新日時:2024-07-21 01:50:19

最終更新日時:2024-07-21 01:50:19

ここではNLP-16Aのアーキテクチャを見れます。(多分)

図をクリックするとそのコンポーネントの詳細ページがある場合は詳細に飛べます。良ければ飛んでみてください。

リンクが切れやすいかもなので切れてたら教えてくだされ。

簡易な構成

簡易な構成

まずは簡易な構成図です。簡単にはアキュムレータを持つ一般的なレジスタマシンです。

一時レジスタとアキュムレータが両方あってちょっと変ですが,これは色々狙いがあってつけたものだったりします。

レジスタファイルはレジスタの集合体のことなのですが実際に中身を見てみると単純にレジスタが並んでいるだけではなく,MUXであったりアドレスデコーダだったりと様々な制御回路が必要になります。こういうところを覗けることが実際にハードで遊ぶ楽しさですね。

詳細な構成

詳細な構成

こちらは詳細なというよりも私がイベント等で一枚の紙ぺらで説明しやすい図になっています。全部盛りで読みづらいものなので参考程度に。

関連するページ

-

NLP-16A NLP-16AはNLP-16をベースとした次世代機.PCBを起こしてNLP-16で見つかったいくつかの欠点を修正を加える予定.

記事作成日時:2023-03-19 17:41:53

最終更新日時:2024-12-06 12:34:38

-

NLP-16A ALU全体の構成 上にある二つの枠がそれぞれ8bitのALUです。このALUを2台並列に接続することで16bit ALUを構成しています。この8bit ALUにはさらにそれぞれの中に1bitのALUがあり,実質的にはこの1bitのALUを16セット並列に並べていることになります。この1bitのALUは回路図中では2から9ページ目にあたります。実行できる演算は以下の通りです。...(以下略)

記事作成日時:2024-07-21 00:23:36

最終更新日時:2024-07-21 01:50:22

-

NLP-16A 命令トランスレータの構成 *****

記事作成日時:2024-07-21 01:22:17

最終更新日時:2024-07-21 01:50:27

-

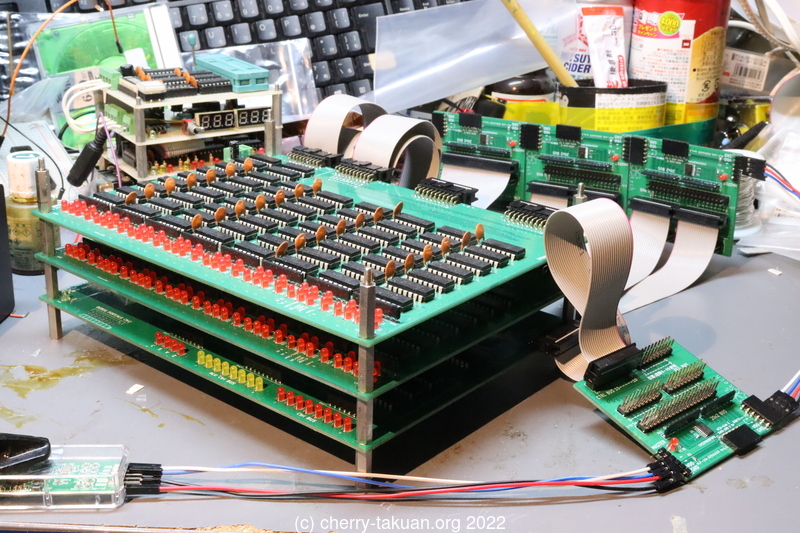

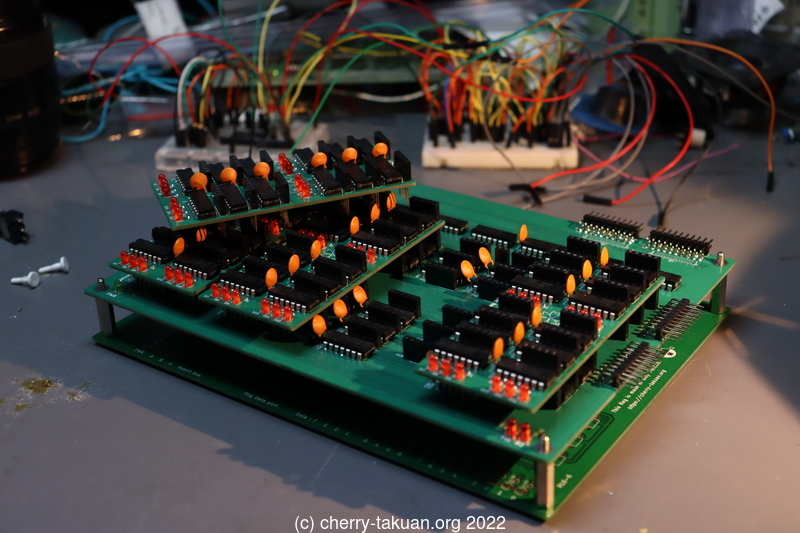

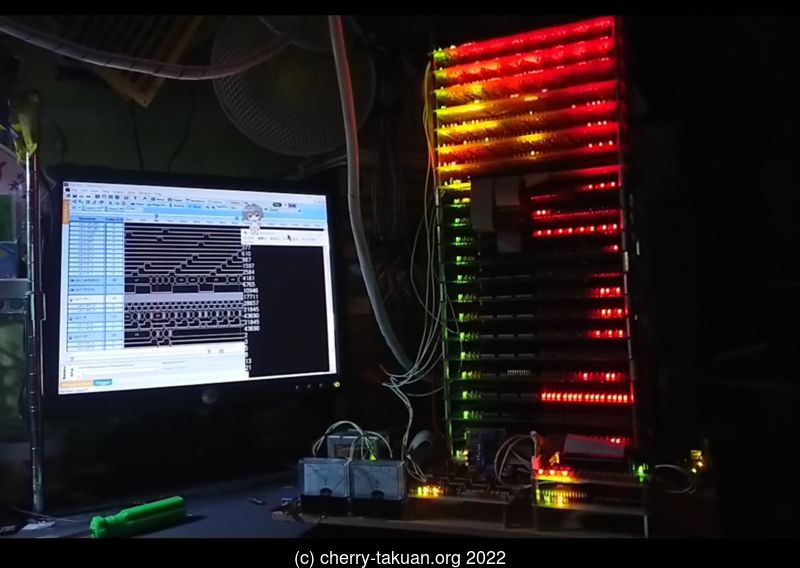

NAND(74HC00)だけで16bitCPUを作る[NLP-16]

このページはNAND素子のICである74HC00のみを用いて16bitCPUを作るという馬鹿みたいなことを纏めたページ。 また、早速だが使っているICは7400ではない。以前は”7400でCPUを作りたい”にしていたが詐欺なので変えた。 使用しているのはC...(以下略)

記事作成日時:2022-02-27 15:47:09

最終更新日時:2023-09-12 03:59:52