最終更新日時:2024-12-06 12:34:38

NLP-16Aの概要

NLP-16Aの概要

NLP-16AはNLP-16をベースとした次世代機.PCBを起こしてNLP-16で見つかったいくつかの欠点を修正を加える予定.

そのため基本的なスペックはNLP-16と同じ.

このデータは暫定です.

| CPUバス幅 | 16bit |

|---|---|

| アドレス幅 | 16bit |

| アーキテクチャ | ストアドプログラム方式 |

| 動作クロック | 設計値600kHz 実測3MHz(分周前) |

| 汎用レジスタ | 16bit幅x4 |

| 命令 | 可変長(1word~3word) |

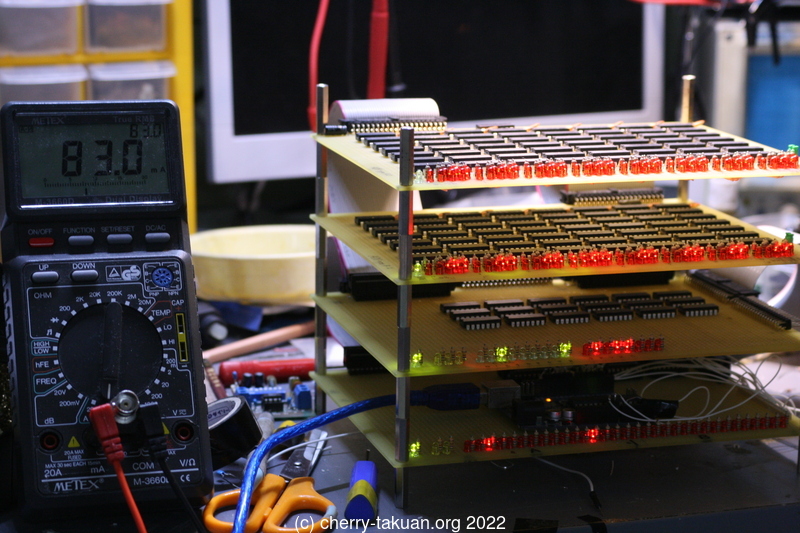

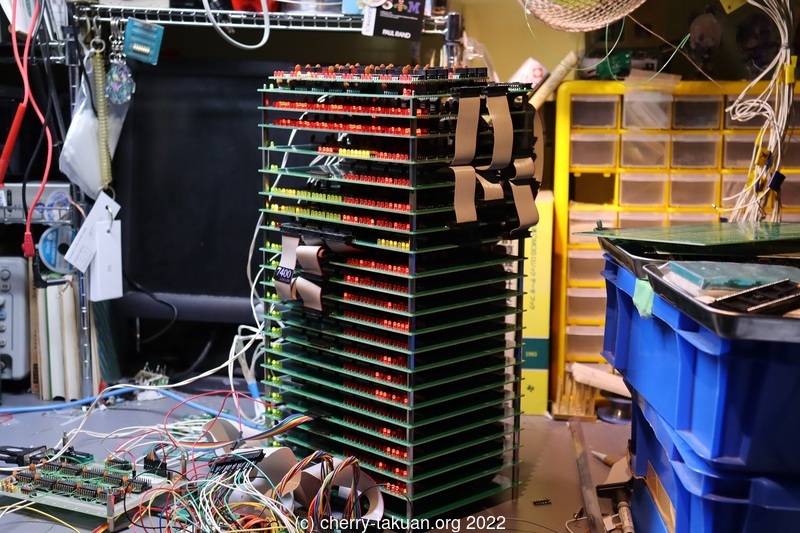

| 74HC00使用数 | 不明.800個くらい |

| 消費電力 | 3W |

現在の作業進捗

現在の作業進捗

ALU製作 → 製作完了

ALU制御 → 製作完了

デバッグ環境構築 → 製作中

レジスタ製作 → 設計中

レジスタ制御 → 設計中

制御 → 設計中

完成しました。

NLP-16の詳説

NLP-16の詳説

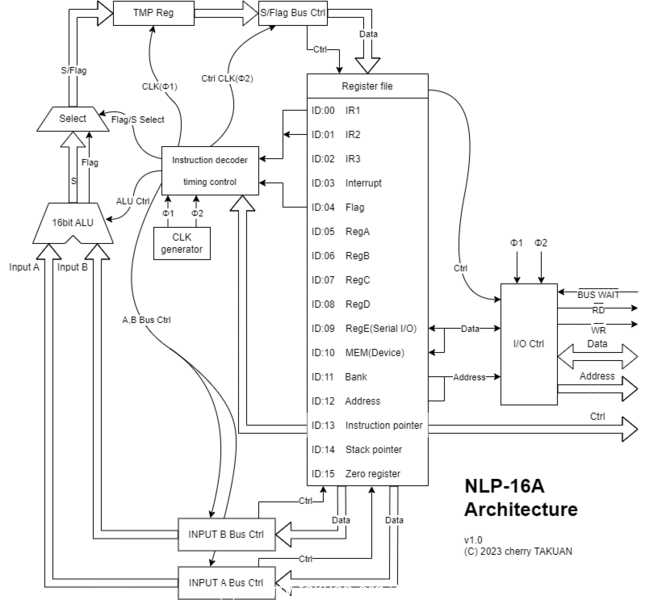

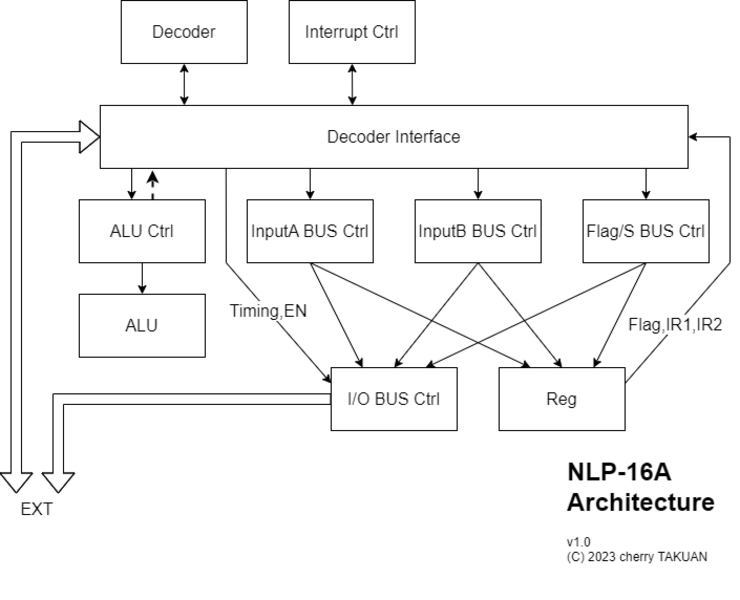

まずはアーキテクチャのブロックチャートをどうぞ

NLP-16から微妙に変わっています

オレオレ仕様な図なんでちょいとわかりにくいかもしれないけど我慢して

クリックすると大きい画像が開きます.

制御系

制御系

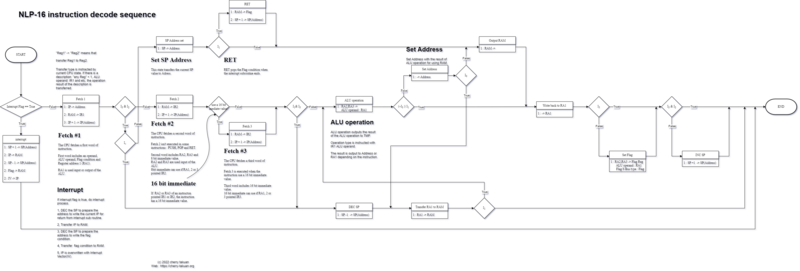

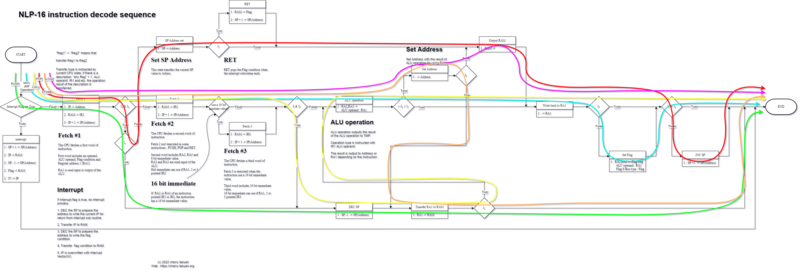

命令デコーダのデコード順序も書いたので良ければ

このフローに従ってデコードしていく(このフローチャートだけ見ても情報が不足している)

色分けをして各種命令のデコード順序を示す.

色分けをして各種命令のデコード順序を示す.

スポンサードリンク

NLP-16で見つかっている欠点

NLP-16で見つかっている欠点

双方向データバスの調停

双方向データバスの調停

ブロックチャートの右端,←Data→の部分はRAMなどの外部デバイスと接続する,双方向のバスになっている.

①双方向のバスではCPU側,外部デバイス側の両方が出力となる可能性がある.両方とも出力になるとデータバス上でショートに近いことが起きるため,そうならないように確実に片側のみ出力になるようにする.

②加えて出力モードを解除されるには若干のタイムラグがあるため両方とも出力がされていない期間(いわゆるデッドタイム)も必要になる.

NLP-16では①はきっちり実現したが,初期の設計が甘く②がクロックに同期した確実なデッドタイムを生成できないことが判明した.

内部データバスのファンアウト

内部データバスのファンアウト

ブロック図中のRegister fileとなっているところの内部ではレジスタそれぞれに対しデータバスY/Flagのデータが通っている.

同じデータをすべてのレジスタに分割しているため,Y/Flag Bus Ctrlの出力に対して16(15)ゲートのNANDが接続されている.

CMOSであるため定常的な電流値は問題ないが,単純に伝送路が1.5mというふざけた長さになっているためいい感じの長さでバッファを入れるべき.

これに関してはすぐになんとかできるため特に重大な不良ではない

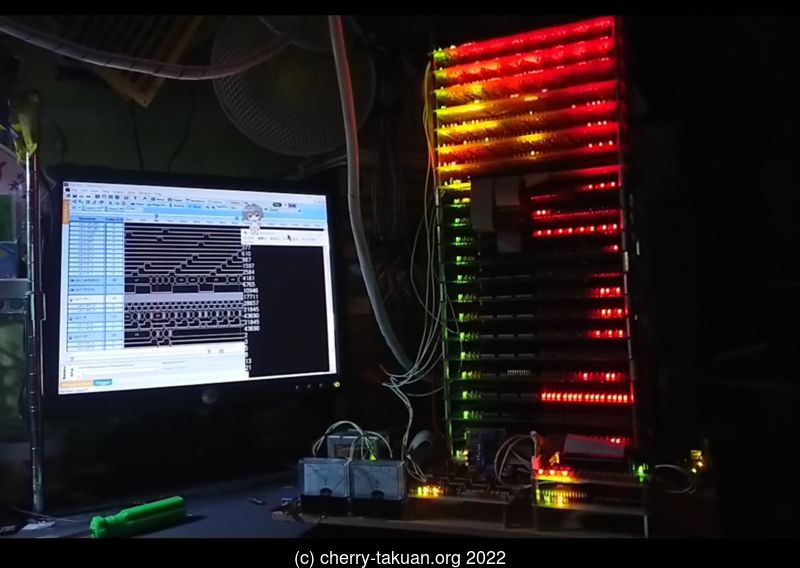

動作のスナップショット

動作のスナップショット

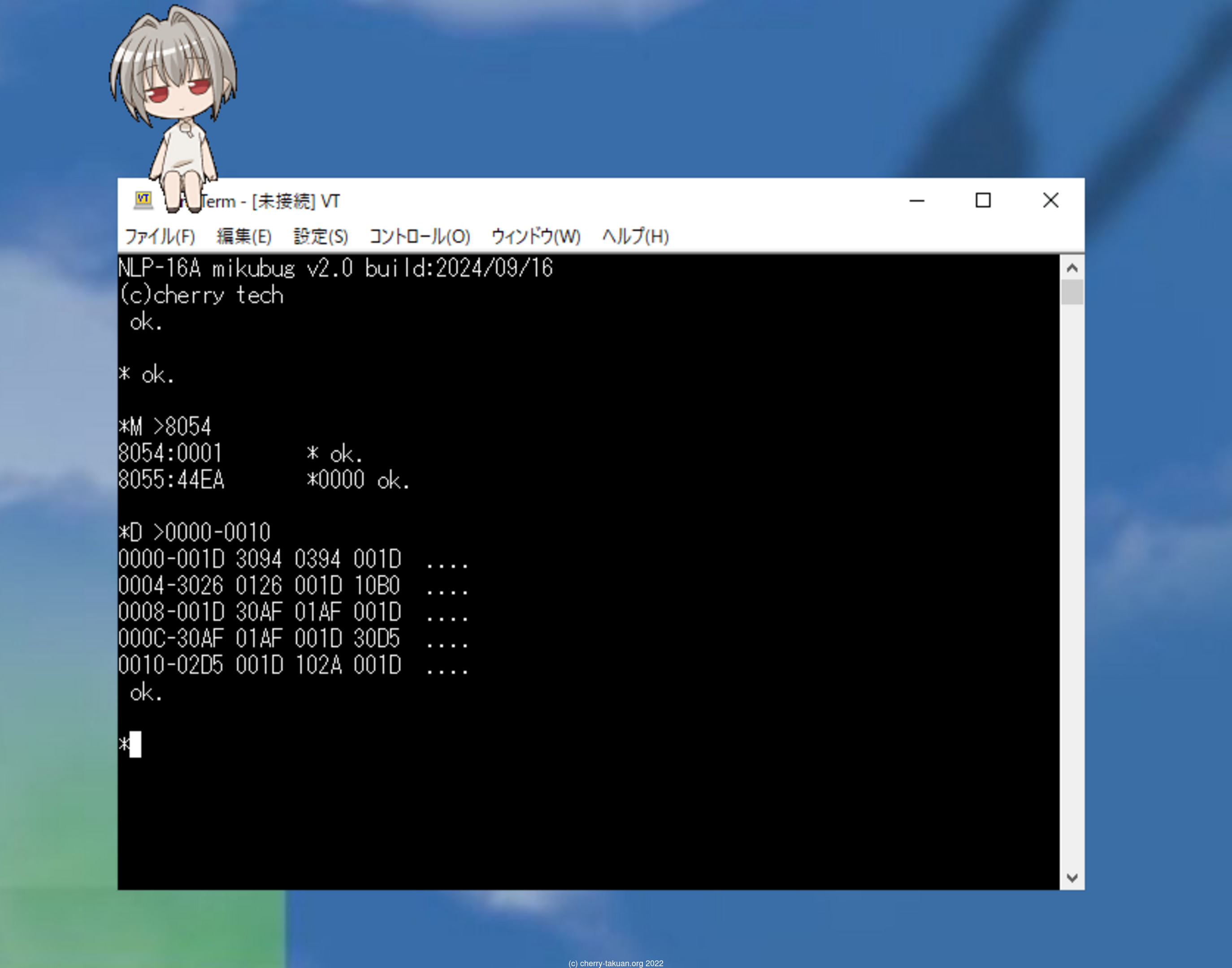

NLP-16Aで動作するモニタプログラム「mikubug」の動作です。Mコマンドで特定アドレスの値を直接変更したりDコマンドで指定範囲のメモリの内容を表示できます。 アプリケーション例

スポンサードリンク

NLP-16A関連のページ

NLP-16A関連のページ

-

NLP-16Aアーキテクチャのページ ここではNLP...(以下略)

記事作成日時:2024-07-20 19:10:43

最終更新日時:2024-07-21 01:50:19

-

NLP-16Aの製作

*****

記事作成日時:2024-08-25 00:02:06

最終更新日時:2024-10-23 23:20:02

関連するページ

-

NAND(74HC00)だけで16bitCPUを作る[NLP-16]

このページはNAND素子のICである74HC00のみを用いて16bitCPUを作るという馬鹿みたいなことを纏めたページ。 また、早速だが使っているICは7400ではない。以前は”7400でCPUを作りたい”にしていたが詐欺なので変えた。 使用しているのはC...(以下略)

記事作成日時:2022-02-27 15:47:09

最終更新日時:2023-09-12 03:59:52

-

NLP-16A NLP-16AはNLP-16をベースとした次世代機.PCBを起こしてNLP-16で見つかったいくつかの欠点を修正を加える予定.

記事作成日時:2023-03-19 17:41:53

最終更新日時:2024-12-06 12:34:38

-

NLP-16Aの製作

*****

記事作成日時:2024-08-25 00:02:06

最終更新日時:2024-10-23 23:20:02

-

NLP-16Aアーキテクチャのページ ここではNLP...(以下略)

記事作成日時:2024-07-20 19:10:43

最終更新日時:2024-07-21 01:50:19